Hardware accelerators can perform specialized computations much faster than general-purpose processors. High-level synthesis (HLS) is the process of turning software programs into synthesized hardware accelerator designs that can be loaded onto a field-programmable gate array (FPGA), which is basically reconfigurable computer hardware.

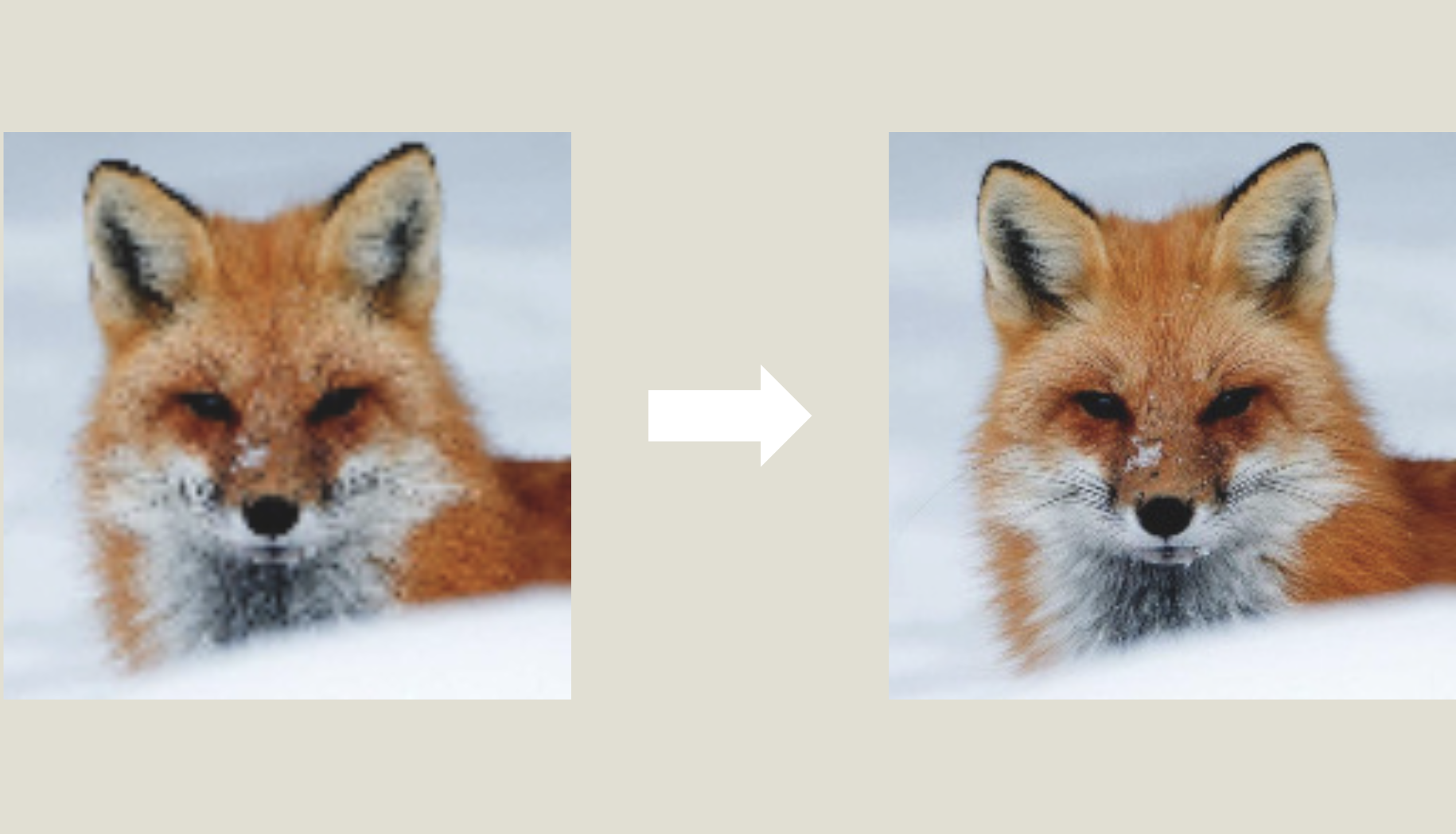

This was my group’s final project for ECE 6775, and we decided to create an accelerator that performs image super-resolution using a simple convolutional neural network consisting of an upsampling layer using nearest-neighbor upsampling and two edge-sharpening convolutional layers. We synthesized and optimized our design using AMD Vivado HLS and ran it on a Zedboard FPGA development board. Watch our final presentation below: